LLM-ASIC's en gespecialiseerde inferentiechips (waarom ze belangrijk zijn)

ASIC's en aangepast silicium verhogen de snelheid en efficiëntie van LLM-inferentie.

De toekomst van AI draait niet alleen om slimmer [modellen](https://www.glukhov.org/nl/rag/embeddings/qwen3-embedding-qwen3-reranker-on-ollama/ “Qwen3 embedding en reranker modellen - state-of-the-art prestaties). Het gaat ook om silicium dat aansluit op de manier waarop deze modellen daadwerkelijk worden aangeboden. Gespecialiseerde hardware voor LLM-inferentie volgt een pad dat doet denken aan de verschuiving in Bitcoin-mining van GPUs naar doelgerichte ASICs, maar met strengere beperkingen omdat modellen en precisie-formules voortdurend evolueren.

Voor meer informatie over doorvoer, latentie, VRAM en benchmarks over verschillende runtime-omgevingen en hardware, zie LLM-prestaties: Benchmarks, bottlenecks & optimalisatie.

Elektrische Imagination - Flux tekst-naar-beeld LLM.

Elektrische Imagination - Flux tekst-naar-beeld LLM.

Waarom LLM’s profiteren van inferentie-specifieke hardware

Large language models hebben AI getransformeerd, maar elke vloeiende reactie is afhankelijk van enorme, voorspelbare stromen van matrixberekeningen en geheugenvkeer. Naarmate de kosten voor inferentie toenemen – en vaak de trainingskosten over de levensduur van een model overtreffen – worden chips die geoptimaliseerd zijn voor het serveren, en niet voor elke denkbare workload, economisch aantrekkelijk.

De analogie met Bitcoin-mining is onvolmaakt maar instructief. Het gaat in beide gevallen om herhalende, goed afgebakende taken waarbij het verwijderen van ongebruikte generaliteit van de chip grote winsten oplevert in doorvoer en joules per nuttige bewerking.

Wat de geschiedenis van Bitcoin-mining suggereert over inferentie-ASICs

Bitcoin-mining evolueerde door vier generaties:

| Era | Hardware | Belangrijk voordeel | Beperking |

|---|---|---|---|

| 2015–2020 | GPUs (CUDA, ROCm) | Flexibiliteit | Energieverbruikend, geheugengebonden |

| 2021–2023 | TPUs, NPUs | Grofkorrelige specialisatie | Nog steeds gericht op training |

| 2024–2025 | Transformer-ASICs | Afgestemd op inferentie met lage bitdiepte | Beperkte generaliteit |

AI volgt een vergelijkbaar pad. Elke overgang verbeterde prestaties en energie-efficiëntie met ordes van grootte.

In tegenstelling tot Bitcoin-ASICs (die alleen SHA-256 berekenen), hebben inferentie-ASICs echter enige flexibiliteit nodig. Modellen evolueren, architecturen veranderen en precisieschema’s verbeteren. De kunst is om net genoeg te specialiseren – de kernpatronen in hardware te gieten terwijl aanpassingsvermogen aan de randen behouden blijft.

Hoe LLM-inferentie verschilt van training (en wat chips benutten)

Inferentie-workloads onthullen patronen waarnaar gespecialiseerde hardware kan richten:

- Lage precisie domineert — 8-bit, 4-bit, zelfs tertiaire of binaire aritmetiek werken goed voor inferentie

- Geheugen is de bottleneck — Het verplaatsen van gewichten en KV-caches verbruikt veel meer energie dan berekening

- Latentie is belangrijker dan doorvoer — Gebruikers verwachten tokens binnen 200 ms

- Massale paralleliteit van verzoeken — Duizenden gelijktijdige inferentieverzoeken per chip

- Voorspelbare patronen — Transformer-lagen zijn zeer gestructureerd en kunnen in hardware worden vastgelegd

- Kansen voor sparstiteit — Modellen maken steeds vaker gebruik van pruning en MoE (Mixture-of-Experts) technieken

Een doelgerichte inferentie-chip kan deze aannames in hardware gieten om 10–50× betere prestaties per watt te bereiken dan universele GPUs.

Wie bouwt silicium geoptimaliseerd voor LLM-inferentie

De markt voor inferentie-ASICs omvat bestaande spelers, wafer-schaal ontwerpen en startups die inzetten op transformer-vormig silicium:

| Bedrijf | Chip / Platform | Specialiteit |

|---|---|---|

| Groq | LPU (Language Processing Unit) | Deterministische doorvoer voor LLM’s |

| Etched AI | Sohu ASIC | In hardware vastgelegde Transformer-engine |

| Tenstorrent | Grayskull / Blackhole | Algemene ML met hoogbandbreedte-mesh |

| Taalas | HC1 (Llama 3.1 8B product) / HC2 roadmap | Model-specifiek “hardcore” silicium; combineert opslag en berekening |

| OpenAI × Broadcom | Custom Inference Chip | Gerucht over lancering in 2026 |

| Intel | Crescent Island | Alleen-inferentie Xe3P GPU met 160GB HBM |

| Cerebras | Wafer-Scale Engine (WSE-3) | Massive on-chip geheugenbandbreedte |

Groot deel hiervan is al in productie in datacenters, niet alleen op presentatieplaatjes. Kleinere teams zoals d-Matrix, Rain AI, Mythic en Tenet volgen ook architecturen die zijn afgestemd op inferentie met lage bitdiepte en gestructureerde sparstiteit.

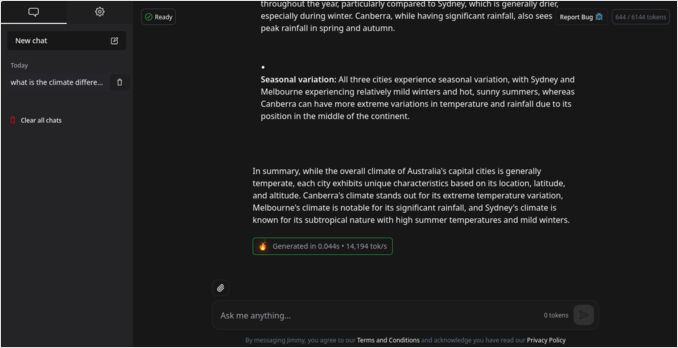

Taalas HC1, Chat Jimmy en ultra-snelle servering van kleine modellen

Taalas is een recent voorbeeld van de school “specialiseer bijna alles”. Het bedrijf stelt dat de grens tussen geheugen en rekenkracht (off-chip DRAM versus on-chip SRAM) de kosten, het stroomverbruik en de engineering-complexiteit voor inferentie domineert, en dat silicium per model – wat zij Hardcore Models noemen – die grens kan laten instorten wanneer een implementatie bereid is om de gewichten en de graaf vast te leggen.

Hun eerste product, HC1, heeft een variant van Llama 3.1 8B in hardware vastgelegd. Die keuze is pragmatisch: het model is klein genoeg om snel op te zetten, openlijk gedocumenteerd en nog steeds nuttig voor veel automatiserings-, classificatie- en ontwerptaken waar ruwe redeneerdiepte minder belangrijk is dan latentie en kosten. Taalas rapporteert een order van 16k–17k gedecodeerde tokens per seconde per gebruiker voor deze configuratie (de methodologie en vergelijkingen van de leverancier staan in hun artikel), naast claims van grote winsten in kapitaal en stroomverbruik vergeleken met conventionele GPU-stacks voor dezelfde modelklasse. Eerste-generatie onderdelen gebruiken agressieve gemengde opslag met lage bitdiepte; het bedrijf beschrijft de overgang naar standaard 4-bit floating formats op HC2 om ruimte te maken voor kwaliteit.

Voor ontwikkelaars die willen voelen wat die doorvoerklasse in de praktijk betekent, runt Taalas een gratis chatbot-demo, Chat Jimmy, en biedt API-toegang via een aanvraagformulier op hun site. Het is expliciet een proof of concept – geen frontier-assistent – maar het illustreert een echt publiek dat misschien kiest voor een bescheiden model op “menselijke cognitieve snelheid” boven een groter model dat traag of duur aanvoelt.

Architectuur van een transformer-inferentie ASIC

Hoe ziet een transformer-geoptimaliseerde chip er eigenlijk uit onder de motorkap?

+--------------------------------------+

| Host-interface |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| On-chip Interconnect (mesh/ring) |

+--------------------------------------+

| Compute Tiles / Cores |

| — Dense matrix multiply units |

| — Low-precision (int8/int4) ALUs |

| — Dequant / Activation units |

+--------------------------------------+

| On-chip SRAM & KV cache buffers |

| — Hot weights, fused caches |

+--------------------------------------+

| Quantization / Dequant Pipelines |

+--------------------------------------+

| Scheduler / Controller |

| — Static graph execution engine |

+--------------------------------------+

| Off-chip DRAM / HBM Interface |

+--------------------------------------+

Belangrijke architectonische kenmerken zijn:

- Compute-kernen — Dense matrix-vermenigvuldigingseenheden geoptimaliseerd voor int8, int4 en tertiaire bewerkingen

- On-chip SRAM — Grote buffers houden warme gewichten en KV-caches vast, wat dure DRAM-toegang minimaliseert

- Streaming-interconnects — Mesh-topologie maakt efficiënte schaalbaarheid over meerdere chips mogelijk

- Quantization-engines — Real-time quantization/dequantization tussen lagen

- Compiler-stack — Vertaalt PyTorch/ONNX-grafen direct naar chip-specifieke micro-operaties

- In hardware vastgelegde attention-kernels — Elimineert overhead van besturingsstroom voor softmax en andere bewerkingen

De ontwerpfilosofie weerspiegelt Bitcoin-ASICs: elk transistor dient de specifieke workload. Geen verspilling van silicium voor functies die inferentie niet nodig heeft.

GPU versus ASIC-benchmarks voor LLM-inferentie

Relevante openbare cijfers tonen hoe gespecialiseerde inferentie-hardware zich kan onderscheiden van universele GPU-stacks voor dezelfde modelfamilies (verifieer altijd de methodologie en batching-aannames voor uw eigen workloads):

| Model | Hardware | Doorvoer (tokens/s) | Tijd tot eerste token | Prestatiemeerdering |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Baseline (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× sneller |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | Consistente 3× |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× sneller |

| Llama-3.1-8B | Taalas HC1 (leverancier) | ~16k–17k decode t/s/gebruiker | — | Aparte as (vast 8B-graaf, niet 70B) |

Bronnen: Groq.com, ArtificialAnalysis.ai, NVIDIA Developer Blog; Taalas HC1-cijfers van het productbericht van het bedrijf.

De Groq-gerelateerde rijen tonen grote winsten in doorvoer en tijd-tot-eerste-token ten opzichte van een high-end GPU-baseline voor grote modellen. De Taalas-rij is geen andere meerdering tegen die 70B-lijnen; het illustreert hoe ver decode-per-gebruiker kan worden geduwd wanneer het model en de graaf in silicium zijn vastgelegd, ten koste van flexibiliteit.

Trade-offs bij het specialiseren van inferentiesilicium

Specialisatie koopt prestaties, maar het introduceert opnieuw product- en engineeringrisico’s:

-

Flexibiliteit versus Efficiëntie. Een volledig vastgestelde ASIC schreeuwt door de transformer-modellen van vandaag, maar kan worstelen met de architecturen van morgen. Wat gebeurt er als attention-mechanismen evolueren of nieuwe modelfamilies ontstaan?

-

Quantization en Nauwkeurigheid. Lagere precisie bespaart enorme hoeveelheden energie, maar het beheren van nauwkeurigheidsverlies vereist geavanceerde quantization-schema’s. Niet alle modellen quantiseren soepel naar 4-bit of lager.

-

Software-ecosysteem. Hardware zonder robuuste compilers, kernels en frameworks is nutteloos. NVIDIA domineert nog steeds grotendeels vanwege het rijpe ecosysteem van CUDA. Nieuwe chipmakers moeten zwaar investeren in software.

-

Kosten en Risico. Het ontwerpen van een chip kost tientallen miljoenen dollars en duurt 12–24 maanden. Voor startups is dit een enorme inzet op architecturale aannames die misschien niet standhouden.

Toch vertalen zelfs efficiëntiewinsten van 2× op hyperschaal naar miljarden besparingen. Voor cloudproviders die miljoenen inferentieverzoeken per seconde verwerken, wordt aangepast silicium steeds ononderhandelbaar.

Een wenslijst voor een LLM-inferentie-chip

| Eigenschap | Ideale specificatie |

|---|---|

| Proces | 3–5nm knooppunt |

| On-chip SRAM | 100MB+ strak gekoppeld |

| Precisie | int8 / int4 / tertiaire native ondersteuning |

| Doorvoer | 500+ tokens/sec (70B model) |

| Latentie | <100ms tijd tot eerste token |

| Interconnect | Laag-latency mesh of optische links |

| Compiler | PyTorch/ONNX → microcode toolchain |

| Energie | <0.3 joules per token |

Kijken vooruit (2026–2030)

Verwacht dat het landschap van inferentiehardware zich zal stratificeren in drie ruwe niveaus:

-

Trainingschips. High-end GPUs zoals NVIDIA B200 en AMD Instinct MI400 zullen training blijven domineren met hun FP16/FP8-flexibiliteit en enorme geheugenbandbreedte.

-

Inferentie-ASICs. In hardware vastgelegde, transformer-accelerators met lage precisie zullen productie-servering op hyperschaal verzorgen, geoptimaliseerd voor kosten en efficiëntie.

-

Edge NPUs. Kleine, ultra-efficiënte chips zullen gequantiseerde LLM’s naar smartphones, voertuigen, IoT-apparaten en robots brengen, waardoor intelligentie op het apparaat mogelijk wordt zonder afhankelijkheid van de cloud.

Naast alleen hardware zullen we zien:

- Hybride clusters — GPUs voor flexibel training, ASICs (of wafer-schaal inferentie-engines) voor efficiënt serveren

- Inferentie-as-a-Service — Hyperscalers die eerste-partij accelerators (AWS Inferentia, Google TPU en anderen) mengen met GPUs

- Hardware-software co-design — Modellen gevormd voor blok-sparstiteit, MoE-routing en quantization-vriendelijke lagen

- Silicium per model of per familie — Bedrijven zoals Taalas die wedden dat sommige implementaties architecturale flexibiliteit zullen ruilen voor extreme kosten en latentie op een bekende graaf

- Open inferentie-API’s — Druk om serverinterfaces draagbaar te houden, zelfs als het silicium dat niet is

Eindgedachten

De “ASIC-isering” van AI-inferentie is al onderweg. Net als Bitcoin-mining evolueerde van CPUs naar gespecialiseerd silicium, volgt AI-implementatie hetzelfde pad.

De volgende revolutie in AI zal niet gaan over grotere modellen — het gaat over betere chips. Hardware geoptimaliseerd voor de specifieke patronen van transformer-inferentie zal bepalen wie AI economisch op schaal kan implementeren.

Net als Bitcoin-miners elke verspilde watt optimaliseerden, zal inferentie-hardware elke laatste FLOP-per-joule uitknijpen. Wanneer dat gebeurt, zal de echte doorbraak niet liggen in de algoritmes — maar in het silicium dat ze uitvoert.

De toekomst van AI wordt in silicium geëtst, transistor voor transistor.

Voor meer benchmarks, hardware-keuzes en prestatie-optimalisatie, bekijk onze LLM-prestaties: Benchmarks, bottlenecks & optimalisatie hub.

Nuttige links

- Groq officiële benchmarks

- Taalas — De weg naar universele AI (HC1, roadmap, filosofie)

- Chat Jimmy — Taalas Llama 3.1 8B demo

- Taalas API-toegang aanvraagformulier

- Artificial Analysis - LLM-prestatie leiderbord

- NVIDIA H100 technische briefing

- Etched AI - Transformer ASIC aankondiging

- Cerebras Wafer-Scale Engine

- NVidia RTX 5080 en RTX 5090 prijzen in Australië - oktober 2025

- LLM-prestaties en PCIe-lanes: Belangrijke overwegingen

- Snelheidstest voor Large Language Models

- Vergelijking van NVidia GPU geschiktheid voor AI

- Is de Quadro RTX 5880 Ada 48GB goed?