LLM-ASICs und spezialisierte Inferenzchips (warum sie wichtig sind)

ASICs und maßgeschneiderte Chips steigern Geschwindigkeit und Effizienz der LLM-Inferenz.

Die Zukunft von KI besteht nicht nur in intelligenteren Modellen. Es geht auch um Silizium, das auf die Art und Weise zugeschnitten ist, wie diese Modelle tatsächlich bereitgestellt werden. Spezialisierte Hardware für die LLM-Inferenz folgt einem Pfad, der an den Wechsel von GPUs zu eigens gebauten ASICs beim Bitcoin-Mining erinnert, jedoch mit schwierigeren Randbedingungen, da sich Modelle und Präzisionsrezepte ständig weiterentwickeln.

Für mehr Informationen zu Durchsatz, Latenz, VRAM und Benchmarks über verschiedene Laufzeiten und Hardware hinweg, siehe LLM-Leistung: Benchmarks, Engpässe & Optimierung.

Elektrische Phantasie - Flux Text-zu-Bild LLM.

Elektrische Phantasie - Flux Text-zu-Bild LLM.

Warum LLMs von inferenzspezifischer Hardware profitieren

Large Language Models haben KI transformiert, aber jede flüssige Antwort hängt von riesigen, vorhersehbaren Strömen von Matrixmathematik und Speicherzugriffen ab. Da die Ausgaben für die Inferenz wachsen – oft über die gesamte Lebensdauer eines Modells den Trainingseinsatz übersteigend – werden Chips, die für den Dienstbetrieb optimiert sind und nicht für jede mögliche Arbeitslast, wirtschaftlich attraktiv.

Die Analogie zum Bitcoin-Mining ist unvollkommen, aber lehrreich. Beide sind repetitive, gut abgegrenzte Aufgaben, bei denen das Entfernen unnötiger Allgemeinheit vom Chip große Gewinne im Durchsatz und an Joule pro nützlicher Operation erbringen kann.

Was die Geschichte des Bitcoin-Minings über Inferenz-ASICs aussagt

Das Bitcoin-Mining entwickelte sich in vier Generationen:

| Ära | Hardware | Hauptvorteil | Einschränkung |

|---|---|---|---|

| 2015–2020 | GPUs (CUDA, ROCm) | Flexibilität | Stromhungrig, speichergebunden |

| 2021–2023 | TPUs, NPUs | Grobe Spezialisierung | Immer noch trainingsorientiert |

| 2024–2025 | Transformer-ASICs | Optimiert für Inferenz mit niedriger Bitbreite | Begrenzte Allgemeinheit |

KI folgt einem ähnlichen Pfad. Jeder Übergang verbesserte Leistung und Energieeffizienz um Größenordnungen.

Im Gegensatz zu Bitcoin-ASICs (die nur SHA-256 berechnen) benötigen Inferenz-ASICs jedoch eine gewisse Flexibilität. Modelle entwickeln sich weiter, Architekturen ändern sich und Präzisschemen verbessern sich. Der Trick besteht darin, genau genug zu spezialisieren – die Kernmuster festzuverdrahten, während man an den Rändern anpassungsfähig bleibt.

Wie sich LLM-Inferenz vom Training unterscheidet (und was Chips ausnutzen)

Inferenz-Arbeitslasten offenbaren Muster, die spezialisierte Hardware gezielt ansprechen kann:

- Niedrige Präzision dominiert – 8-Bit, 4-Bit, sogar ternäre oder binäre Arithmetik funktionieren gut für die Inferenz

- Speicher ist der Engpass – Das Verschieben von Gewichten und KV-Caches verbraucht weit mehr Energie als die Berechnung

- Latenz ist wichtiger als Durchsatz – Benutzer erwarten Tokens innerhalb von unter 200 ms

- Massive Parallelität der Anfragen – Tausende gleichzeitige Inferenzanfragen pro Chip

- Vorhersehbare Muster – Transformer-Schichten sind hochstrukturiert und können fest verdrahtet werden

- Möglichkeiten für Sparsity (Dünnbesetztheit) – Modelle nutzen zunehmend Pruning und MoE (Mixture-of-Experts)-Techniken

Ein eigens gebauter Inferenz-Chip kann diese Annahmen fest verdrahten, um eine 10–50× bessere Leistung pro Watt im Vergleich zu allgemeinen GPUs zu erreichen.

Wer Inferenz-Silizium für LLMs optimiert baut

Der Markt für Inferenz-ASICs erstreckt sich über etablierte Unternehmen, Wafer-Scale-Designs und Startups, die auf Transformer-optimiertes Silizium wetten:

| Unternehmen | Chip / Plattform | Spezialität |

|---|---|---|

| Groq | LPU (Language Processing Unit) | Determinierter Durchsatz für LLMs |

| Etched AI | Sohu ASIC | Fest verdrahteter Transformer-Engine |

| Tenstorrent | Grayskull / Blackhole | Allgemeiner ML mit hochbreitbandigem Mesh |

| Taalas | HC1 (Llama 3.1 8B Produkt) / HC2 Roadmap | Modell-spezifisches „Hardcore"-Silizium; kombiniert Speicher und Rechenleistung |

| OpenAI × Broadcom | Custom Inference Chip | Gerüchte über Rollout 2026 |

| Intel | Crescent Island | Nur-Inferenz Xe3P GPU mit 160GB HBM |

| Cerebras | Wafer-Scale Engine (WSE-3) | Massive On-Die Speicherbandbreite |

Viel davon ist bereits in Produktions-Rechenzentren im Einsatz, nicht nur in Präsentationen. Kleinere Teams wie d-Matrix, Rain AI, Mythic und Tenet verfolgen ebenfalls Architekturen, die auf Inferenz mit niedriger Bitbreite und strukturierte Sparsity abgestimmt sind.

Taalas HC1, Chat Jimmy und ultra-schnelle Bereitstellung kleiner Modelle

Taalas ist ein jüngstes Beispiel der Schule „spezialisiere fast alles". Das Unternehmen argumentiert, dass die Grenze zwischen Speicher und Rechenleistung (Off-Chip-DRAM gegenüber On-Chip-SRAM) Kosten, Energieverbrauch und Ingenieurskomplexität für die Inferenz dominiert, und dass Silizium pro Modell – was sie als Hardcore Models bezeichnen – diese Grenze kollabieren lassen kann, wenn eine Bereitstellung bereit ist, die Gewichte und den Graphen zu fixieren.

Ihr erstes lieferbares Produkt, HC1, verdrahtet eine Llama 3.1 8B-Variante fest. Diese Wahl ist pragmatisch: Das Modell ist klein genug, um schnell hochgefahren zu werden, ist offen dokumentiert und dennoch für viele Automatisierungs-, Klassifizierungs- und Entwurfsaufgaben nützlich, bei denen die rohe Tiefe der Schlussfolgerung weniger wichtig ist als Latenz und Kosten. Taalas berichtet von einer Größenordnung von 16k–17k dekodierten Tokens pro Sekunde pro Benutzer für diese Konfiguration (Herstellermethodik und Vergleiche erscheinen in ihrem Bericht), zusammen mit Behauptungen großer Gewinne bei Kapital und Energie im Vergleich zu herkömmlichen GPU-Stacks für dieselbe Modellklasse. Bauteile der ersten Generation verwenden aggressive gemischte Speicher mit niedriger Bitbreite; das Unternehmen beschreibt den Übergang zu Standard-4-Bit-Gleitkommaformaten auf HC2, um Spielraum bei der Qualität zurückzugewinnen.

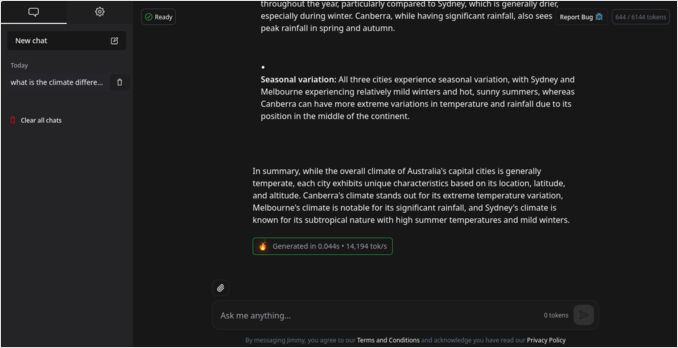

Für Entwickler, die fühlen wollen, was diese Durchsatzklasse in der Praxis bedeutet, betreibt Taalas einen kostenlosen Chatbot-Demo, Chat Jimmy, und bietet API-Zugang über ein Antragsformular auf ihrer Website. Es ist explizit ein Proof of Concept – kein Frontline-Assistent – aber es veranschaulicht ein echtes Publikum, das einem bescheidenen Modell mit „menschlicher Kognitionsgeschwindigkeit" gegenüber einem größeren Modell, das sich träge oder teuer anfühlt, den Vorzug geben könnte.

Architektur eines Transformer-Inferenz-ASICs

Wie sieht ein Transformer-optimierter Chip tatsächlich unter der Haube aus?

+--------------------------------------+

| Host-Schnittstelle |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| On-Chip-Interconnect (Mesh/Ring) |

+--------------------------------------+

| Compute-Tiles / Kerne |

| — Dense-Matrix-Multiplikationseinheiten |

| — Low-Precision (int8/int4) ALUs |

| — Dequant / Aktivierungseinheiten |

+--------------------------------------+

| On-Chip SRAM & KV-Cache-Puffer |

| — Heiße Gewichte, verschmolzene Caches |

+--------------------------------------+

| Quantisierungs- / Dequantisierungs-Pipelines |

+--------------------------------------+

| Scheduler / Controller |

| — Engine für statische Graphausführung |

+--------------------------------------+

| Off-Chip DRAM / HBM-Schnittstelle |

+--------------------------------------+

Wichtige architektonische Merkmale umfassen:

- Rechenkern – Dense-Matrix-Multiplikationseinheiten, optimiert für int8, int4 und ternäre Operationen

- On-Chip SRAM – Große Puffer halten heiße Gewichte und KV-Caches, was teure DRAM-Zugriffe minimiert

- Streaming-Interconnects – Mesh-Topologie ermöglicht effizientes Skalieren über mehrere Chips

- Quantisierungs-Engines – Echtzeit-Quantisierung/Dequantisierung zwischen den Schichten

- Compiler-Stack – Übersetzt PyTorch/ONNX-Graphen direkt in chip-spezifische Mikro-Befehle

- Fest verdrahtete Attention-Kerne – Eliminiert Overhead für Steuerungsfluss bei Softmax und anderen Operationen

Die Designphilosophie spiegelt Bitcoin-ASICs wider: Jeder Transistor dient der spezifischen Arbeitslast. Kein verschwendetes Silizium für Funktionen, die die Inferenz nicht benötigt.

GPU gegenüber ASIC-Benchmarks für LLM-Inferenz

Repräsentative öffentliche Zahlen zeigen, wie spezialisierte Inferenz-Hardware von allgemeinen GPU-Stacks bei denselben Modellfamilien Abstand gewinnen kann (prüfen Sie immer die Methodik und Batch-Voraussetzungen für Ihre eigenen Arbeitslasten):

| Modell | Hardware | Durchsatz (Tokens/s) | Zeit bis zum ersten Token | Leistungsmultiplikator |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Basis (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× schneller |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | Konsistent 3× |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× schneller |

| Llama-3.1-8B | Taalas HC1 (Hersteller) | ~16k–17k Decode-T/s/User | — | Separate Achse (festes 8B-Graph, nicht 70B) |

Quellen: Groq.com, ArtificialAnalysis.ai, NVIDIA Developer Blog; Taalas HC1-Zahlen stammen aus dem Produktpost des Unternehmens.

Die auf Groq fokussierten Zeilen zeigen große Gewinne im Durchsatz und in der Zeit bis zum ersten Token gegenüber einer High-End-GPU-Basislinie bei großen Modellen. Die Taalas-Zeile ist kein weiterer Multiplikator gegenüber diesen 70B-Zeilen; sie veranschaulicht, wie weit die Dekodierung pro Benutzer getrieben werden kann, wenn das Modell und der Graph im Silizium fixiert sind, auf Kosten der Flexibilität.

Kompromisse bei der Spezialisierung von Inferenz-Silizium

Spezialisierung kauft Leistung, führt aber Produkt- und Ingenieursrisiken wieder ein:

-

Flexibilität vs. Effizienz. Ein vollständig fixierter ASIC rast durch die heutigen Transformer-Modelle, könnte aber bei den Architekturen von morgen Schwierigkeiten haben. Was passiert, wenn sich Attention-Mechanismen weiterentwickeln oder neue Modellfamilien entstehen?

-

Quantisierung und Genauigkeit. Niedrigere Präzision spart massive Mengen an Energie, aber die Verwaltung des Genauigkeitsverlusts erfordert ausgefeilte Quantisierungsschemata. Nicht alle Modelle quantisieren sich elegant auf 4-Bit oder darunter.

-

Software-Ökosystem. Hardware ohne robuste Compiler, Kerne und Frameworks ist nutzlos. NVIDIA dominiert immer noch weitgehend wegen des ausgereiften Ökosystems von CUDA. Neue Chip-Hersteller müssen stark in Software investieren.

-

Kosten und Risiko. Das Tape-Out eines Chips kostet zig Millionen Dollar und dauert 12–24 Monate. Für Startups ist dies eine massive Wette auf architektonische Annahmen, die nicht haltbar sein könnten.

Dennoch übersetzen sich auf Hyperskala selbst 2×-Effizienzgewinne in Milliarden an Einsparungen. Für Cloud-Anbieter, die Millionen von Inferenzanfragen pro Sekunde abwickeln, wird maßgeschneidertes Silizium zunehmend unverhandelbar.

Eine Wunschliste für einen LLM-Inferenz-Chip

| Merkmal | Ideale Spezifikation |

|---|---|

| Prozess | 3–5nm-Knoten |

| On-Chip SRAM | 100MB+ eng gekoppelt |

| Präzision | int8 / int4 / ternäre native Unterstützung |

| Durchsatz | 500+ Tokens/sec (70B-Modell) |

| Latenz | <100ms Zeit bis zum ersten Token |

| Interconnect | Niedrige Latenz Mesh oder optische Links |

| Compiler | PyTorch/ONNX → Mikrcode-Toolchain |

| Energie | <0,3 Joule pro Token |

Ausblick (2026–2030)

Erwarten Sie, dass sich die Landschaft der Inferenz-Hardware in drei grobe Ebenen stratifiziert:

-

Training-Chips. High-End-GPUs wie NVIDIA B200 und AMD Instinct MI400 werden das Training mit ihrer FP16/FP8-Flexibilität und massiver Speicherbandbreite weiter dominieren.

-

Inferenz-ASICs. Fest verdrahtete, niedrige-Präzision-Transformer-Acceleratoren werden den Produktivdienstbetrieb im Hyperscale-Bereich übernehmen, optimiert für Kosten und Effizienz.

-

Edge-NPUs. Kleine, ultra-effiziente Chips werden quantisierte LLMs zu Smartphones, Fahrzeugen, IoT-Geräten und Robotern bringen und On-Device-Intelligenz ohne Cloud-Abhängigkeit ermöglichen.

Über die Hardware hinaus werden wir sehen:

- Hybride Cluster – GPUs für flexibles Training, ASICs (oder Wafer-Scale-Inferenz-Engines) für effiziente Bereitstellung

- Inferenz-als-Dienst – Hyperscaler mischen eigene Acceleratoren (AWS Inferentia, Google TPU und andere) mit GPUs

- Hardware-Software-Co-Design – Modelle, die für Block-Sparsity, MoE-Routing und quantisierungsfreundliche Schichten geformt sind

- Silizium pro Modell oder pro Familie – Unternehmen wie Taalas wetten darauf, dass einige Bereitstellungen architektonische Flexibilität gegen extreme Kosten und Latenz auf einem bekannten Graphen eintauschen werden

- Offene Inferenz-APIs – Druck, Bereitstellungsschnittstellen portabel zu halten, auch wenn das Silizium nicht portabel ist

Abschließende Gedanken

Die „ASIC-isierung" der KI-Inferenz ist bereits im Gange. Genau wie das Bitcoin-Mining von CPUs zu spezialisiertem Silizium evolvierte, folgt auch der KI-Einsatz demselben Pfad.

Die nächste Revolution in der KI wird nicht um größere Modelle gehen – es wird um bessere Chips gehen. Hardware, die auf die spezifischen Muster der Transformer-Inferenz optimiert ist, wird bestimmen, wer KI wirtschaftlich im großen Maßstab bereitstellen kann.

Genau wie Bitcoin-Miner jede verschwendete Watt optimiert haben, wird Inferenz-Hardware jeden letzten FLOP-pro-Joule ausquetschen. Wenn das passiert, wird der wahre Durchbruch nicht in den Algorithmen liegen – er wird im Silizium liegen, das sie ausführt.

Die Zukunft der KI wird in Silizium geätzt, Transistor für Transistor.

Für weitere Benchmarks, Hardware-Entscheidungen und Leistungsoptimierung, besuchen Sie unser Hub LLM-Leistung: Benchmarks, Engpässe & Optimierung.

Nützliche Links

- Groq Offizielle Benchmarks

- Taalas — Der Weg zu allgegenwärtiger KI (HC1, Roadmap, Philosophie)

- Chat Jimmy — Taalas Llama 3.1 8B Demo

- Taalas API-Zugangs-Antragsformular

- Artificial Analysis - LLM-Leistungs-Leaderboard

- NVIDIA H100 Technisches Briefing

- Etched AI - Transformer-ASIC-Ankündigung

- Cerebras Wafer-Scale Engine

- NVidia RTX 5080 und RTX 5090 Preise in Australien - Oktober 2025

- LLM-Leistung und PCIe-Lanes: Wichtige Überlegungen

- Large Language Models Speed Test

- Vergleich der Eignung von NVidia GPUs für KI

- Ist der Quadro RTX 5880 Ada 48GB gut?